# Linear & Switching Voltage Regulator Handbook

**ON Semiconductor**<sup>™</sup>

### **Linear & Switching Voltage Regulator Handbook**

HB206/D Rev. 4, Feb–2002

© SCILLC, 2002 Previous Edition © 1989 "All Rights Reserved"

SWITCHMODE, POWERTAP and TMOS are trademarks of Semiconductor Components Industries, LLC (SCILLC).

All brand names and product names appearing in this document are registered trademarks or trademarks of their respective holders.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031

Phone: 81–3–5740–2700 Email: r14525@onsemi.com

**ON Semiconductor Website**: http://onsemi.com For additional information, please contact your local

Sales Representative.

## Linear & Switching Voltage Regulator Applications Information

#### In Brief . . .

In most electronic systems, voltage regulation is required for various functions. Today's complex electronic systems are requiring greater regulating performance, higher efficiency and lower parts count. Present integrated circuit and power package technology has produced IC voltage regulators which can ease the task of regulated power supply design, provide the performance required and remain cost effective. Available in a growing variety, ON Semiconductor offers a wide range of regulator products from fixed and adjustable voltage types to special–function and switching regulator control ICs.

This handbook describes ON Semiconductor's voltage regulator products and provides information on applying these products. Basic Linear regulator theory and switching regulator topologies have been included along with practical design examples. Other relevant topics include trade—offs of Linear versus switching regulators, series pass elements for Linear regulators, switching regulator component design considerations, heatsinking, construction and layout, power supply supervision and protection, and reliability.

|                                                                  | Page |

|------------------------------------------------------------------|------|

| Basic Linear Regulator Theory                                    | 6    |

| Selecting a Linear IC Voltage Regulator                          | 15   |

| Linear Regulator Circuit Configuration and Design Considerations | 18   |

| Series Pass Element Considerations for Linear Regulators         | 29   |

| Linear Regulator Construction and Layout                         | 37   |

| Linear Regulator Design Example                                  | 59   |

| Linear Regulator Circuit Troubleshooting Check List              | 62   |

| Designing the Input Supply                                       | 63   |

| An Introduction to Switching Power Supplies                      | 69   |

| Switching Regulator Topologies                                   | 74   |

| Switching Regulator Component Design Tips                        | 83   |

| Basic Switching Power Supply Configurations                      | 88   |

| Switching Regulator Design Examples                              | 96   |

| Power Supply Supervisory and Protection Considerations           | 97   |

| Heatsinking                                                      | 106  |

#### **TABLE OF CONTENTS**

|            |                                                                  | Page |

|------------|------------------------------------------------------------------|------|

| Section 1. | Basic Linear Regulator Theory                                    | 6    |

|            | IC Voltage Regulator                                             | 6    |

|            | Voltage Reference                                                | 6    |

|            | The Error Amplifier                                              | 10   |

|            | The "Regulator within a Regulator" Approach                      | 13   |

|            |                                                                  |      |

| Section 2. | Selecting a Linear IC Voltage Regulator                          | 15   |

|            | Selecting the Type of Regulator                                  | 15   |

|            | Positive versus Negative Regulators                              | 15   |

|            | Three–Terminal, Fixed Output Regulators                          | 15   |

|            | Three–Terminal, Adjustable Output Regulators                     | 17   |

|            | Selecting an IC Regulator                                        | 17   |

|            | Selecting an IC Regulator                                        | 17   |

| Section 3. | Linear Pegulater Circuit Configuration and Design Considerations | 18   |

| Section 3. | Linear Regulator Circuit Configuration and Design Considerations |      |

|            | Positive, Adjustable Regulator                                   | 18   |

|            | Negative, Adjustable Regulator                                   | 22   |

|            | Positive, Fixed Output Regulator                                 | 22   |

|            | Negative, Fixed Output Regulator                                 | 25   |

|            | General Design Considerations                                    | 27   |

| 0          | Out to Book Floor of Occasion of Albace Book Indian              | 00   |

| Section 4. | Series Pass Element Considerations for Linear Regulators         | 29   |

|            | Series Pass Element Configurations                               | 29   |

|            | Series Pass Element Specifications                               | 30   |

|            | Current Limiting Techniques                                      | 31   |

|            | Constant Current Limiting                                        | 31   |

|            | Foldback Current Limiting                                        | 34   |

|            | Paralleling Series Pass Elements                                 | 36   |

|            |                                                                  |      |

| Section 5. | Linear Regulator Construction and Layout                         | 37   |

|            | General Layout and Component Placement Considerations            | 37   |

|            | Ground Loops and Remote Voltage Sensing                          | 37   |

|            | Mounting Considerations for Power Semiconductors                 | 39   |

|            | Insulation Considerations                                        | 43   |

|            | Fastener and Hardware Characteristics                            | 47   |

|            | Thermal System Evaluation                                        | 55   |

|            | Appendix A: Thermal Resistance Concepts                          | 56   |

|            | Appendix B: Measurement of Interface Thermal Resistance          | 57   |

| 0          | III a a Bara Liva Barba E a a da                                 |      |

| Section 6. | Linear Regulator Design Example                                  | 59   |

|            | IC Regulator Selection                                           | 59   |

|            | Circuit Configuration                                            | 59   |

|            | Determination of Component Values                                | 59   |

|            | Determination of Input Voltage                                   | 60   |

|            | Selection of Series Pass Element                                 | 60   |

|            | Q1 Heatsink Calculation                                          | 61   |

|            | Clamp Diode                                                      | 61   |

|            | Construction Input Supply Design                                 | 61   |

|            |                                                                  |      |

| Section 7. | Linear Regulator Circuit Troubleshooting Check List              | 62   |

### **TABLE OF CONTENTS (Continued)**

|             |                                                                               | Page     |

|-------------|-------------------------------------------------------------------------------|----------|

| Section 8.  | Designing the Input Supply                                                    | 63       |

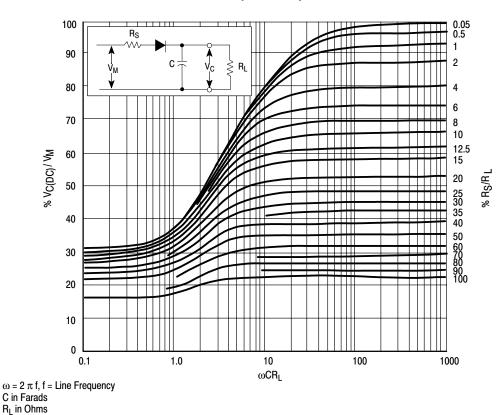

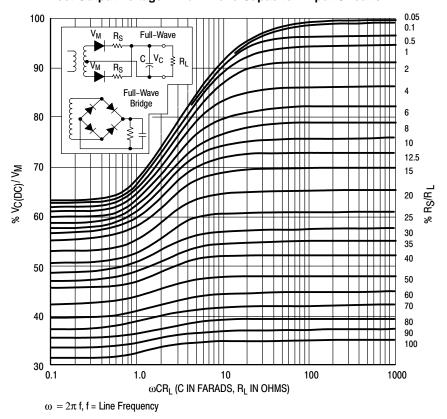

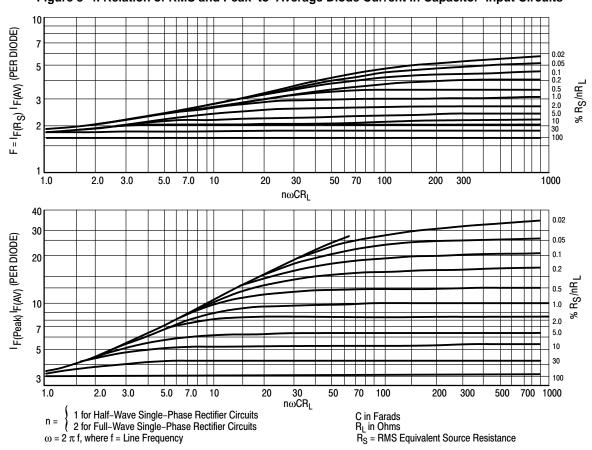

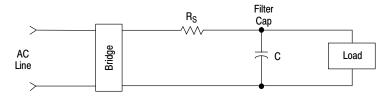

|             | Design of Capacitor–Input Filters                                             | 64       |

|             | Surge Current                                                                 | 66       |

|             | Design Procedure                                                              | 67       |

|             | Design Example                                                                | 68       |

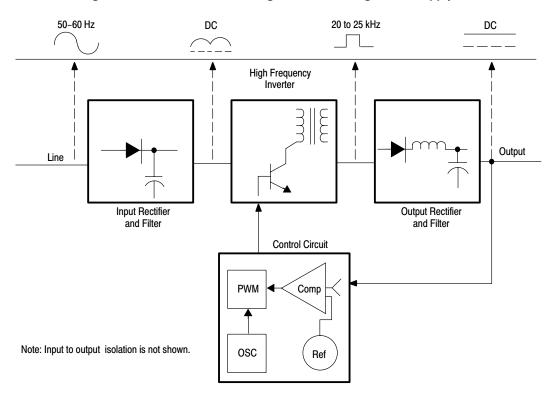

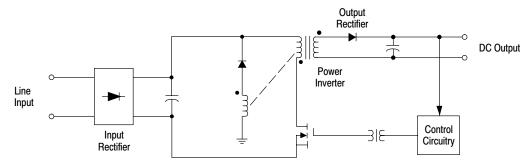

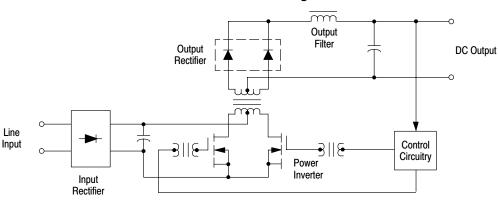

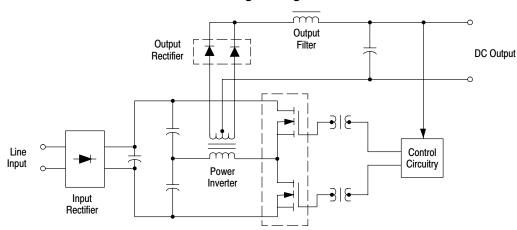

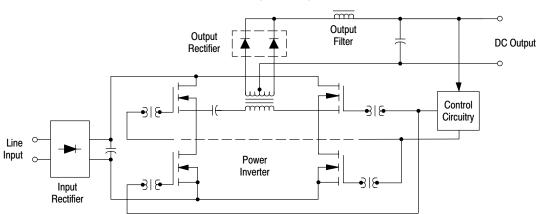

| Section 9.  | An Introduction to Switching Power Supplies                                   | 69       |

| 00011011 01 | Comparison with Linear Regulators                                             | 69       |

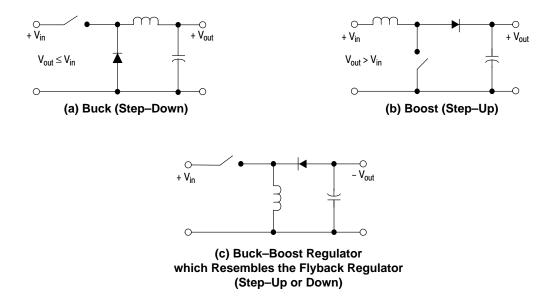

|             | Basic Configurations                                                          | 70       |

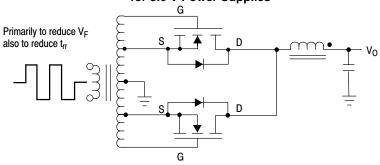

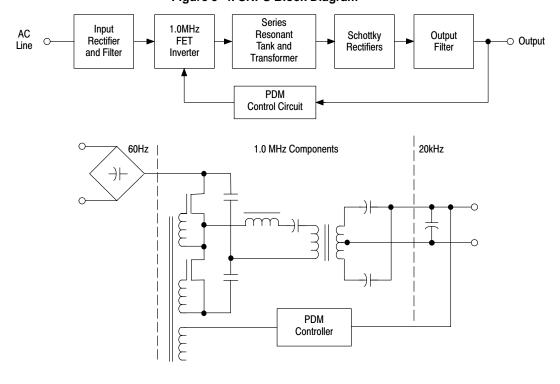

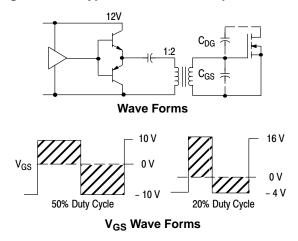

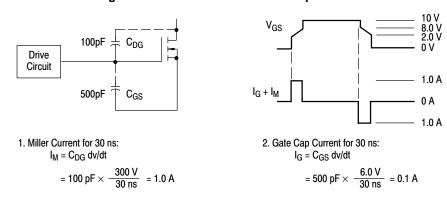

|             | The Future                                                                    | 72       |

|             |                                                                               |          |

| Section 10. | Switching Regulator Topologies                                                | 74       |

|             | FET and Bipolar Drive Considerations                                          | 74       |

|             | Control Circuits                                                              | 76       |

|             | Overvoltage Protection                                                        | 77       |

|             | Surge Current Protection                                                      | 79<br>79 |

|             | Transformer Design                                                            | 79<br>81 |

|             | Titles Capacitos Considerations                                               | 01       |

| Section 11. | Switching Regulator Component Design Tips                                     | 83       |

|             | Transistors                                                                   | 83       |

|             | Zener and Mosorb Transient Suppressors                                        | 85       |

|             | Rectifiers                                                                    | 85       |

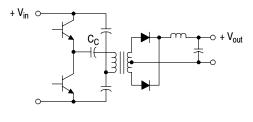

| Section 12. | Basic Switching Power Supply Configurations                                   | 88       |

|             | Flyback and Forward Converters                                                | 88       |

|             | Push-Pull and Bridge Converters                                               | 91       |

|             | Half and Full Bridge                                                          | 94       |

| Section 13. | Switching Regulator Design Examples                                           | 96       |

| Section 14. | Dower Sumply Supervisory and Protection Considerations                        | 97       |

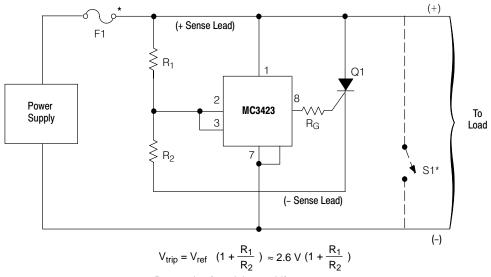

| Section 14. | Power Supply Supervisory and Protection Considerations  The Crowbar Technique | 97       |

|             | SCR Considerations                                                            | 98       |

|             | The Sense and Drive Circuit                                                   | 99       |

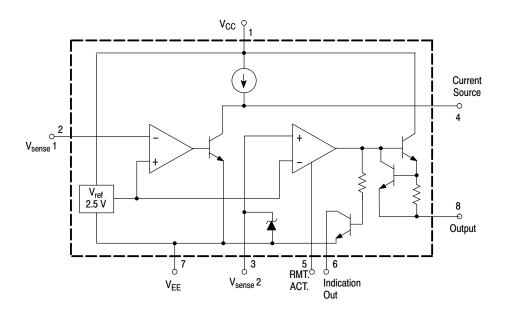

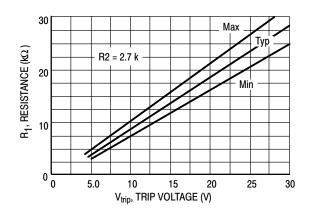

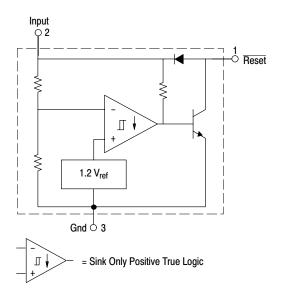

|             | MC3425 Power Supply Supervisory Circuit                                       | 103      |

|             | MC34064 and MC34164 Series                                                    | 105      |

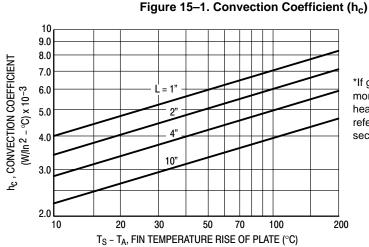

| Section 15. | Heatsinking                                                                   | 106      |

| Section 13. | The Thermal Equation                                                          | 106      |

|             | Selecting a Heatsink                                                          | 107      |

|             | Commercial Heatsinks                                                          | 107      |

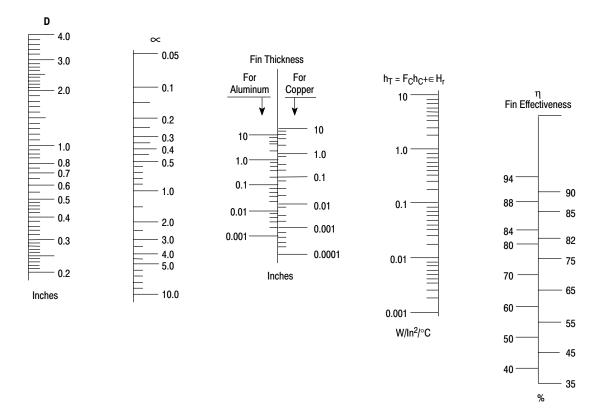

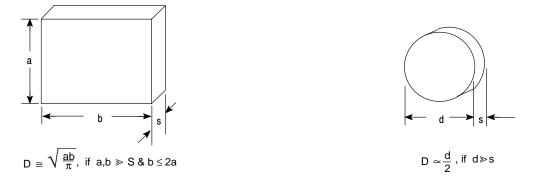

|             | Custom Heatsink Design                                                        | 107      |

|             | Heatsink Design Example                                                       | 112      |

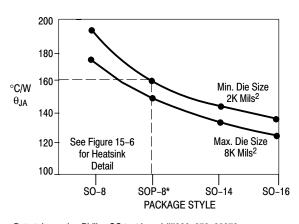

|             | SOIC Miniature IC Plastic Package                                             | 112      |

|             | Thermal Characteristics of SOIC Packages                                      | 113      |

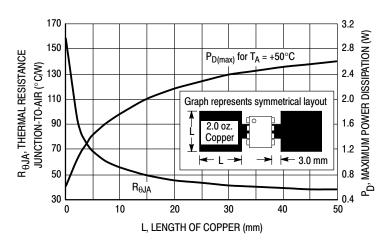

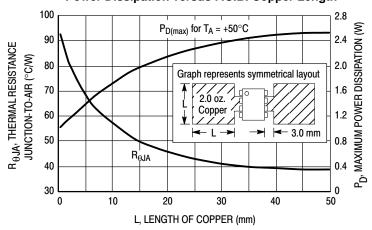

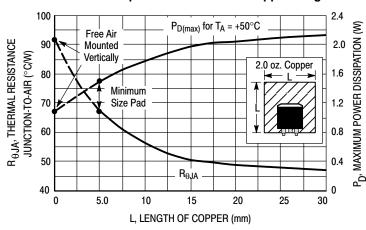

|             | SOP–8 and SOP–16L Packaged Devices                                            | 113      |

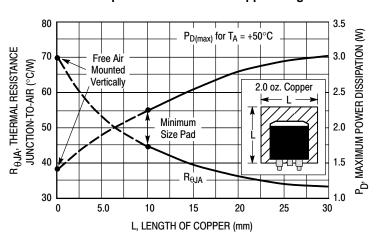

|             | Thermal Characteristics of DPAK and D <sup>2</sup> PAK Packages               | 114      |

|             |                                                                               |          |

# SECTION 1 BASIC LINEAR REGULATOR THEORY

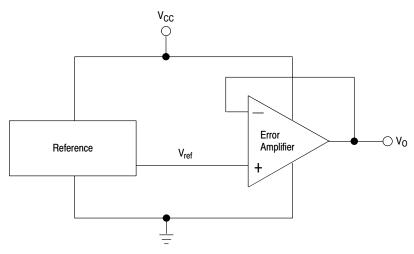

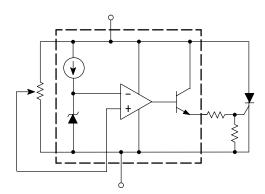

#### A. IC Voltage Regulator

The basic functional block diagram of an integrated circuit voltage regulator is shown in Figure 1–1. It consists of a stable reference, whose output voltage is  $V_{ref}$ , and a high gain error amplifier. The output voltage ( $V_O$ ), is equal to or a multiple of  $V_{ref}$ . The regulator will tend to keep  $V_O$  constant by sensing any changes in  $V_O$  and trying to return it to its original value. Therefore, the ideal voltage regulator could be considered a voltage source with a constant output voltage. However, in practice the IC regulator is better represented by the model shown in Figure 1–2.

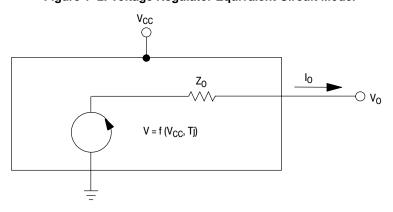

In this figure, the regulator is modeled as a voltage source with a positive output impedance ( $Z_O$ ). The value of the voltage source (V) is not constant; instead it varies with changes in supply voltage ( $V_{CC}$ ) and with changes in IC junction temperature ( $T_J$ ) induced by changes in ambient temperature and power dissipation. Also, the regulator output voltage ( $V_O$ ) is affected by the voltage drop across  $Z_O$ , caused by the output current ( $I_O$ ). In the following text, the reference and amplifier sections will be described, and their contributions to the changes in the output voltage analyzed.

#### **B. Voltage Reference**

Naturally, the major requirement for the reference is that it be stable; variations in supply voltage or junction temperature should have little or no effect on the value of the reference voltage ( $V_{ref}$ ).

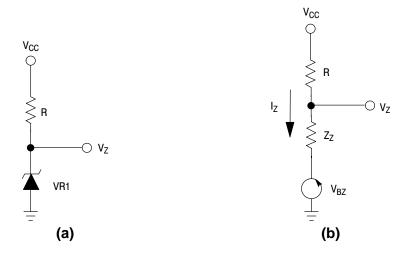

#### 1. Zener Diode Reference

The simplest form of a voltage reference is shown in Figure 1–3a. It consists of a resistor and a zener diode. The zener voltage ( $V_Z$ ) is used as the reference voltage. In order to determine  $V_Z$ , consider Figure 1–3b. The zener diode (VR1) of Figure 1–3a has been replaced with its equivalent circuit model and the value of  $V_Z$  is therefore given by (at a constant junction temperature):

$$V_Z = V_{BZ} + I_Z Z_Z = V_{BZ} + \left(\frac{V_{CC} - V_{BZ}}{R + Z_Z}\right) Z_Z$$

(1)

where:  $V_{BZ}$  = zener breakdown voltage

$I_7$  = zener current

$Z_Z$  = zener impedance at  $I_Z$ .

Note that changes in the supply voltage give rise to changes in the zener current, thereby changing the value of the reference voltage  $(V_Z)$ .

Figure 1–1. Voltage Regulator Functional Block Diagram

Figure 1–2. Voltage Regulator Equivalent Circuit Model

Figure 1-3. Zener Diode Reference

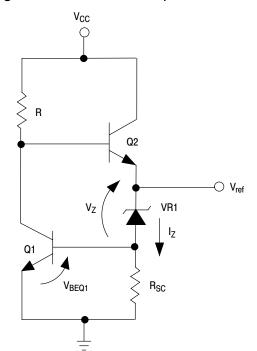

#### 2. Constant Current — Zener Reference

The effect of zener impedance can be minimized by driving the zener diode with a constant current as shown in Figure 1–4. The value of the zener current is largely independent of  $V_{CC}$  and is given by:

$$I_Z = \frac{V_{BEQ1}}{R_{SC}} \tag{2}$$

where:  $V_{BEQ1}$  = base-emitter voltage of Q1.

This gives a reference voltage of:

$$V_{ref} = V_Z + V_{BEQ1} = V_{BZ} + I_Z Z_Z + V_{BEQ1}$$

(3)

where  $I_Z$  is constant and given by Equation 2.

The reference voltage (about 7.0 V) of this configuration is therefore largely independent of supply voltage variations. This configuration has the additional benefit of better temperature stability than that of a simple resistor—zener reference.

Referring back to Figure 1–3a, it can be seen that the reference voltage temperature stability is equal to that of the zener diode, VR1. The stability of zener diodes used in most integrated circuitry is about + 2.2 mV/°C or  $\approx 0.04\%$ /°C (for a 6.2 V zener). If the junction temperature varies 100°C, the zener or reference voltage would vary 4%. A variation this large is usually unacceptable.

However, the circuit of Figure 1–4 does not have this drawback. Here the positive 2.2 mV/ $^{\circ}$ C temperature coefficient (TC) of the zener diode is offset by the negative 2.2 mV/ $^{\circ}$ C TC of the V<sub>BE</sub> of Q1. This results in a reference voltage with very stable temperature characteristics.

Figure 1–4. Constant Current (Zener Reference)

#### 3. Bandgap Reference

Although very stable, the circuit of Figure 1–4 does have a disadvantage in that it requires a supply voltage of 9.0 V or more. Another type of stable reference which requires only a few volts to operate was described by Widlar<sup>(1)</sup> and is shown in Figure 1–5. In this circuit V<sub>ref</sub> is given by:

$$V_{\text{ref}} = V_{\text{BEQ3}} + I_2 R_2 \tag{4}$$

where:

$$I_2 = \frac{V_{BEQ1} - V_{BEQ2}}{R_1}$$

(neglecting base currents)

The change in V<sub>ref</sub> with junction temperature is given by:

$$\Delta V_{\text{ref}} = \Delta V_{\text{BE3}} + \left\{ \frac{\Delta V_{\text{BEQ1}} - \Delta V_{\text{BEQ2}}}{R_1} \right\} R_2$$

(5)

It can be shown that,

$$\Delta V_{BEO1} = \Delta T_{I} K \ln I_{1}$$

(6)

and,

$$\Delta V_{BEQ2} = \Delta T_J K \ln I_2$$

(7)

where: K = a constant

$\Delta T_J$  = change in junction temperature

and,  $I_1 > I_2$

Combining (5), (6), and (7)

$$\Delta V_{\text{ref}} = \Delta V_{\text{BEQ3}} + \Delta T_{\text{J}} K \quad \left(\frac{R_2}{R_1}\right) \ln \frac{I_1}{I_2}$$

(8)

Since  $\Delta$  V<sub>BEQ3</sub> is negative, and with I<sub>1</sub> > I<sub>2</sub>, In I<sub>1</sub>/I<sub>2</sub> is positive, the net change in V<sub>ref</sub> with temperature variations can be made to equal zero by appropriately selecting the values of I<sub>1</sub>, R<sub>1</sub>, and R<sub>2</sub>.

V<sub>CC</sub>

R<sub>3</sub>

V<sub>ref</sub>

V<sub>BEQ1</sub>

V<sub>BEQ2</sub>

R<sub>1</sub>

Figure 1-5. Bandgap Reference

#### C. The Error Amplifier

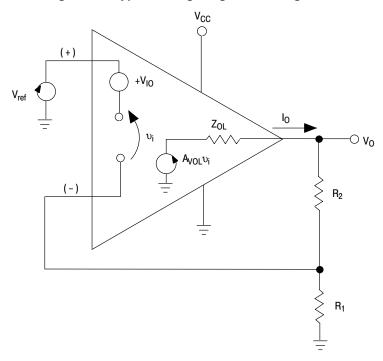

Given a stable reference, the error amplifier becomes the determining factor in integrated circuit voltage regulator performance. Figure 1–6 shows a typical differential error amplifier in a voltage regulator configuration. With a constant supply voltage ( $V_{CC}$ ) and junction temperature, the output voltage is given by:

$$V_{O} = A_{VOL} v_{i} - Z_{OL} I_{O} = A_{VOL} \{ (V_{ref} \pm V_{IO}) - V_{O} \beta \} - Z_{OL} I_{O}$$

(9)

where: A<sub>VOL</sub> = amplifier open loop gain

V<sub>IO</sub> = input offset voltage

$Z_{OL}$  = open loop output impedance

$$β = \frac{R_1}{R_1 + R_2}$$

= feedback ratio (β is always ≤1)

I<sub>O</sub> = output current

$v_i$ = true differential input voltage

Manipulating Equation 9:

$$V_{O} = \frac{(V_{ref} \pm V_{IO}) - \frac{Z_{OL}}{A_{VOL}} I_{O}}{\beta + \frac{1}{A_{VOI}}}$$

(10)

Note that if the amplifier open loop gain is infinite, this expression reduces to:

$$V_{O} = \frac{1}{\beta} (V_{ref} \pm V_{IO}) = (V_{ref} \pm V_{IO}) (1 + \frac{R_{2}}{R_{1}})$$

(11)

The output voltage can thus be set any value equal to or greater than  $(V_{ref} \pm V_{IO})$ . Note also that if  $A_{VOL}$  is not infinite, with constant output current (a non-varying output load), the output voltage can still be "tweaked–in" by varying  $R_1$  and  $R_2$ , even though  $V_O$  will not exactly equal that given by Equation 11.

Assuming a stable reference and a finite value of  $A_{VOL}$ , inaccuracy of the output voltage can be traced to the following amplifier characteristics:

#### 1. Amplifier Input Offset Voltage Drift

The input transistors of integrated circuit amplifiers are usually not perfectly matched. As in operational amplifiers, this is expressed in terms of an input offset voltage ( $V_{IO}$ ). At a given temperature, this effect can be nulled out of the desired output voltage by adjusting  $V_{ref}$  or  $1/\beta$ . However,  $V_{IO}$  drifts with temperature, typically  $\pm$  5.0  $\mu$ V/°C to +15  $\mu$ V/°C, causing a proportional change in the output voltage. Closer matching of the internal amplifier input transistors minimizes this effect, as does selecting a feedback ratio ( $\beta$ ) to be close to unity.

#### 2. Amplifier Power Supply Sensitivity

Changes in regulator output voltage due to power supply voltage variations can be attributed to two amplifier performance parameters: power supply rejection ratio (PSRR) and common mode rejection ratio (CMRR). In modern integrated circuit regulator amplifiers, the utilization of constant current sources gives such large values of PSRR that this effect on  $V_O$  can usually be neglected. However, supply voltage changes can affect the output voltage since these changes appear as common mode voltage changes, and they are best measured by the CMRR.

Figure 1-6. Typical Voltage Regulator Configuration

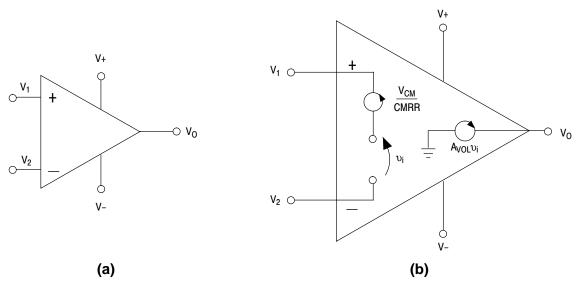

The definition of common mode voltage (V<sub>CM</sub>), illustrated by Figure 1–7a, is:

$$V_{CM} = \left[\frac{V_{1} + V_{2}}{2}\right] - \left[\frac{(V+) + (V-)}{2}\right]$$

(12)

where:  $V_1$  = voltage on amplifier noninverting input

V<sub>2</sub> = voltage on amplifier inverting input

V+ = positive supply voltageV- = negative supply voltage

Figure 1–7. Definition of Common Mode Voltage Error

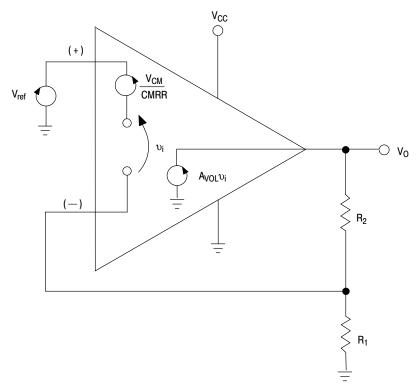

Figure 1–8. Common Mode Regulator Effects

In an ideal amplifier, only the differential input voltage  $(V_1-V_2)$  has any effect on the output voltage; the value of  $V_{CM}$  would not effect the output. In fact,  $V_{CM}$  does influence the amplifier output voltage. This effect can be modeled as an additional voltage offset at the amplifier input equal to  $V_{CM}$ /CMRR as shown in Figures 1–7b and 1–8. The latter figure is the same configuration as Figure 1–6, with amplifier input offset voltage and output impedance deleted for clarity and common mode voltage effects added. The output voltage of this configuration is given by:

$$V_{O} = A_{VOL} v_{i} = A_{VOL} \left( V_{ref} - \frac{V_{CM}}{CMRR} - \beta V_{O} \right)$$

(13)

Manipulating,

$$V_{O} = \frac{\left(V_{ref} - \frac{V_{CM}}{CMRR}\right)}{\beta + \frac{1}{A_{VOL}}}$$

(14)

where:

$$V_{CM} = V_{ref} - \frac{V_{CC}}{2}$$

(15)

and, CMRR = common mode rejection ratio

It can be seen from Equations (14) and (15) that the output can vary when  $V_{CC}$  varies. This can be reduced by designing the amplifier to have a high  $A_{VOL}$ , a high CMRR, and by choosing the feedback ratio ( $\beta$ ) to be unity.

#### 3. Amplifier Output Impedance

Referring back to Equation (9), it can be seen that the equivalent regulator output impedance (Z<sub>O</sub>) is given by:

$$Z_{O} = \frac{\Delta V_{O}}{\Delta I_{O}} \simeq \frac{Z_{OL}}{\beta A_{VOL}}$$

(16)

This impedance must be as low as possible, in order to minimize load current effects on the output voltage. This can be accomplished by lowering  $Z_{OL}$ , choosing an amplifier with high  $A_{VOL}$ , and by selecting the feedback ratio ( $\beta$ ) to be unity.

A simple way of lowering the effective value of  $Z_{OL}$  is to make an impedance transformation with an emitter follower, as shown in Figure 1–9. Given a change in output current ( $\Delta I_O$ ) the amplifier will see a change of only  $\Delta I_O/h_{FEQ1}$  in its output current ( $I_O'$ ). Therefore, ( $Z_{OL}$ ) in Equation (16) has been effectively reduced to  $Z_{OL}/h_{FEQ1}$ , reducing the overall regulator output impedance ( $Z_O$ ).

#### D. The Regulator within a Regulator Approach

In the preceding text, we have analyzed the sections of an integrated circuit voltage regulator and determined how they contribute to its non–ideal performance characteristics. These are shown in Table 1–1 along with procedures which minimize their effects.

It can be seen that in all cases regulator performance can be improved by selecting  $A_{VOL}$  as high as possible and  $\beta=1$ . Since a limit is soon approached in how much  $A_{VOL}$  can be practically obtained in an integrated circuit amplifier, selecting a feedback ratio ( $\beta$ ) equal to unity is the only viable way of improving total regulator performance, especially in reducing regulator output impedance. However, this method presents a basic problem to the regulator designer. If the configuration of Figure 1–6 is used, the output voltage cannot be adjusted to a value other than  $V_{ref}$ . The solution is to utilize a different regulator configuration known as the *regulator within a regulator* approach. (2) Its greatest benefit is in reducing total regulator output impedance.

(+)

V<sub>ref</sub>

Z<sub>OL</sub>

I<sub>O</sub>

V<sub>O</sub>

R<sub>2</sub>

R<sub>1</sub>

Figure 1–9. Emitter Follower Output

Table 1-1

| V <sub>O</sub> Changes<br>Section | Effect Can Be<br>Induced By: | Minimized By Selecting:                                                                                                                             |

|-----------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Deferred                          | V <sub>CC</sub>              | Constant current–zener method     Bandgap reference                                                                                                 |

| Reference                         | T <sub>J</sub>               | Bandgap reference     TC compensated zener method                                                                                                   |

|                                   | Vcc                          | <ul> <li>High CMRR amplifier</li> <li>High A<sub>VOL</sub> amplifier</li> <li>β = 1</li> </ul>                                                      |

| Amplifier                         | TJ                           | <ul> <li>Low V<sub>IO</sub> drift amplifier</li> <li>High A<sub>VOL</sub> amplifier</li> <li>β = 1</li> </ul>                                       |

|                                   | lo                           | <ul> <li>Low Z<sub>OL</sub> amplifier</li> <li>High A<sub>VOL</sub> amplifier</li> <li>Additional emitter follower output</li> <li>β = 1</li> </ul> |

As shown in Figure 1–10, amplifier A1 sets up a voltage  $(V_1)$  given by:

$$V_1 \simeq V_{\text{ref}} \left( 1 + \frac{R_2}{R_1} \right) \tag{17}$$

$V_1$  now serves as the reference voltage for amplifier A2, whose output voltage ( $V_0$ ) is given by:

$$V_0 \simeq V_1 \simeq V_{ref} \left(1 + \frac{R_2}{R_1}\right)$$

(18)

Note that the output impedance of A2, and therefore the regulator output impedance, has been minimized by selecting A2's feedback factor to be unity; and that output voltage can still be set at voltages greater than  $V_{ref}$  by adjusting  $R_1$  and  $R_2$ .

V<sub>ref</sub> + A1 + +

Figure 1-10. The "Regulator within a Regulator" Configuration

<sup>(1)</sup>Widlar, R. J., New Developments in IC Voltage Regulators, IEEE Journal of Solid State Circuits, Feb.1971, Vol. SC-6, pgs. 2-7.

<sup>(2)</sup>Tom Fredericksen, IEEE Journal of Solid State Circuits, Vol. SC-3, Number 4, Dec. 1968, A Monolithic High Power Series Voltage Regulator.

#### **SECTION 2**

#### SELECTING A LINEAR IC VOLTAGE REGULATOR

#### A. Selecting the Type of Regulator

There are five basic linear regulator types; positive, negative, fixed output, tracking and floating regulators. Each has its own particular characteristics and best uses, and selection depends on the designer's needs and trade—offs in performance and cost.

#### 1. Positive Versus Negative Regulators

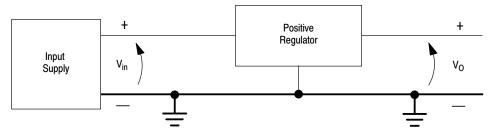

In most cases, a positive regulator is used to regulate positive voltages and a negative regulator negative voltages. However, depending on the system's grounding requirements, each regulator type may be used to regulate the "opposite" voltage.

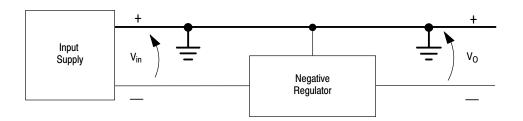

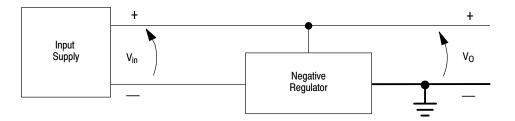

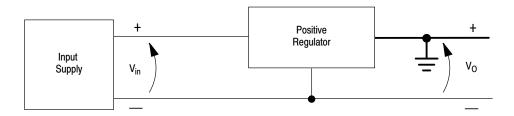

Figures 2–1a and 2–1b show the regulators used in the conventional and obvious mode. Note that the ground reference for each (indicated by the heavy line) is continuous. Several positive regulators could be used with the same input supply to deliver several voltages with common grounds; negative regulators may be utilized in a similar manner.

If no other common supplies or system components operate off the input supply to the regulator, the circuits of Figures 2–1c and 2–1d may be used to regulate positive voltages with a negative regulator and vice versa. In these configurations, the input supply is essentially floated, i.e., neither side of the input is tied to the system ground.

There are methods of utilizing positive regulators to obtain negative output voltages without sacrificing ground bus continuity. However, these methods are only possible at the expense of increased circuit complexity and cost. An example of this technique is shown in Section 3.

#### 2. Three-Terminal, Fixed Output Regulators

These regulators offer the designer a simple, inexpensive way to obtain a source of regulated voltage. They are available in a variety of positive or negative output voltages and current ranges.

The advantages of these regulators are:

- a) Easy to use.

- b) Internal overcurrent and thermal protection.

- c) No circuit adjustments necessary.

- d) Low cost.

#### Their disadvantages are:

- a) Output voltage cannot be precisely adjusted. (Methods for obtaining adjustable outputs are shown in Section 3).

- b) Available only in certain output voltages and currents.

- c) Obtaining greater current capability is more difficult than with other regulators. (Methods for obtaining greater output currents are shown in Section 3.)

Figure 2-1. Regulator Configurations

(a) Positive Output Using Positive Regulator

(b) Negative Output Using Negative Regulator

(c) Positive Output Using Negative Regulator

(d) Negative Output Using Positive Regulator

#### 3. Three-Terminal, Adjustable Output Regulators

Like the three–terminal fixed regulators, the three–terminal adjustable regulators are easy and inexpensive to use. These devices provide added flexibility with output voltage adjustable over a wide range, from 1.2 V to nearly 40 V, by means of an external, two–resistor voltage divider. A variety of current ranges from 100 mA to 3.0 A are available.

#### B. Selecting an IC Regulator

Once the type of regulator is decided upon, the next step is to choose a specific device. To provide higher currents than are available from monolithic technologies, an IC regulator will often be used as a driver to a boost transistor. This complicates the selection and design task, as there are now several overlapping solutions to many of the design problems.

Unfortunately, there is no exact step-by-step procedure that can be followed which will lead to the ideal regulator and circuit configuration for a specific application. The regulating circuit that is finally accepted will be a compromise between such factors as performance, cost, size and complexity. Because of this, the following general design procedure is suggested:

- 1. Select the regulators which meet or exceed the requirements for line regulation, load regulation, TC of the output voltage and operating ambient temperature range. At this point, do not be overly concerned with the regulator capabilities in terms of output voltage, output current, SOA and special features.

- 2. Next, select application circuits from Section 3 which meet the requirements for output current, output voltage, special features, etc. Preliminary designs using the chosen regulators and circuit configurations are then possible. From these designs a judgement can be made by the designer as to which regulator circuit configuration combination best meets his or her requirements in terms of cost, size and complexity.

#### **SECTION 3**

## LINEAR REGULATOR CIRCUIT CONFIGURATION AND DESIGN CONSIDERATIONS

Once the IC regulators, which meet the designer's performance requirements, have been selected, the next step is to determine suitable circuit configurations. Initial designs are devised and compared to determine the IC regulator/circuit configuration that best meets the designer's requirements. In this section, several circuit configurations and design equations are given for the various regulator ICs. Additional circuit configurations can be found on the device data sheets. Organization is first by regulator type and then by variants, such as current boost. Each circuit diagram has component values for a particular voltage and current regulator design.

- A. Positive, Adjustable

- B. Negative, Adjustable

- C. Positive, Fixed

- D. Negative, Fixed

- E. Tracking

- F. Special

- 1. Obtaining Extended Output Voltage Range

- 2. Electronic Shutdown

- G. General Design Considerations

It should be noted that all circuit configurations shown have constant current limiting. If foldback limiting is desired, see Section 4C for techniques and design equations.

#### A. Positive, Adjustable Output IC Regulator Configurations

#### 1. Basic Regulator Configurations

#### Positive Three-Terminal Adjustables

These adjustables, comprised of the LM317L, LM317, and LM350 series devices range in output currents of 100 mA, 500 mA, 1.5 A, and 3.0 A respectively. All of these devices utilize the same basic circuit configuration as shown in Figure 3–1A.

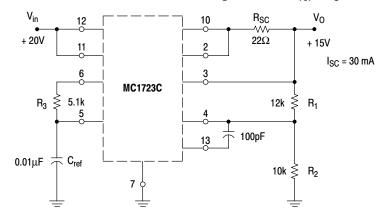

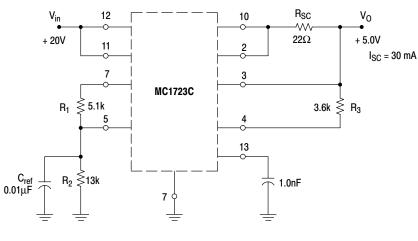

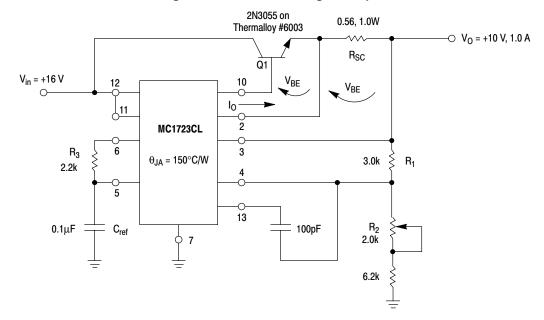

#### MC1723C

The basic circuit configurations for the MC1723C regulator are shown in Figures 3–2A and 3–3A. For output voltages from  $\simeq 7.0$  V to 37 V the configuration of Figure 3–2A can be used, while Figure 3–3A can be used to obtain output voltages from 2.0 V to  $\simeq 7.0$  V.

#### 2. Output Current Boosting

If output currents greater than those available from the basic circuit configurations are desired, the current boost circuits shown in this section can be used. The output currents which can be obtained with this configurations are limited only by capabilities of the external pass element(s).

Figure 3–1A. Basic Configuration for Positive, Adjustable Output Three–Terminal Regulators

Cin: required if regulator is located an appreciable distance from power supply filter.

C<sub>O</sub>: improves transient response.

C<sub>Adj</sub>: improves Ripple Rejection.

$$V_{out} = 1.25 \ V \quad 1 + \left( \ \frac{R_2}{R_1} \right) + I_{Adj} \ R_2$$

Since  $I_{Adj}$  is controlled to less than 100  $\mu\text{A},$  the error associated with this term is negligible in most applications.

Figure 3–2A. MC1723C Basic Circuit Configuration for  $V_{ref} \leq V_0 \leq 37~V$

$$R_{SC} \cong ~ \frac{0.66\,\text{V}}{I_{SC}} ~;~ 10\,\text{k}\Omega < R_1 + R_2 < 100\,\text{k}\Omega$$

$$R_{3}\cong R_{1} \parallel R_{2}$$

;  $0 \leq C_{ref} \leq 0.1~\mu F$

$$R_2 = \ \, \frac{V_{ref}}{V_0} \ \, \left( R_1 + R_2 \right) \approx \ \, \frac{7.0 \ V}{V_0} \ \, \left( R_1 + R_2 \right) \label{eq:R2}$$

Values shown are for a 15 V, 30 mA regulator using an MC1723CP for a  $T_{A(max)}$  = 25°C.

Figure 3–3A. MC1723C Basic Circuit Configuration for 2.0 V  $\leq$  V<sub>O</sub>  $\leq$  V<sub>ref</sub>

$$R_{SC} \simeq \quad \frac{0.66V}{I_{SC}} \ ; 10 \ k\Omega < R_1 + R_2 < 100 \ k\Omega \label{eq:RSC}$$

$$R_2 = \ \frac{V_0}{V_{ref}} \ (R_1 + R_2) \simeq \ \frac{V_0}{7.0 \ V} \ (R_1 + R_2)$$

$$R_3 = R_1 \parallel R_2$$

;  $0 \le C_{ref} \le 0.1 \mu F$

Values shown are for a 5.0 V, 30 mA regulator using an MC1723CP for a  $T_{A(max)} = 70^{\circ}C$ .

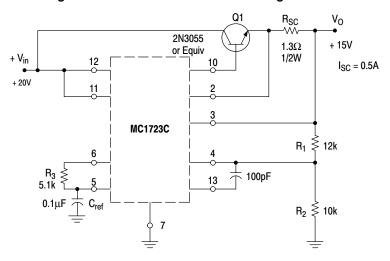

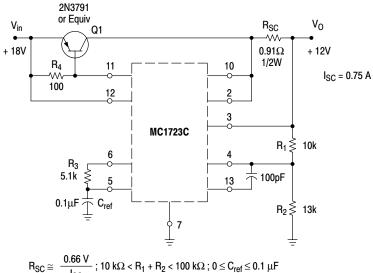

To obtain greater output currents with the MC1723C the configurations shown in Figures 3–4A and 3–5A can be used. Figure 3–4A uses an NPN external pass element, while a PNP is used in Figure 3–5A.

Figure 3-4A. MC1723C NPN Boost Configuration

$$R_{SC} \cong ~ \frac{0.66 \, V}{I_{SC}} ~; 10 \, k\Omega < R_1 + R_2 < 100 \, k\Omega \label{eq:RSC}$$

$$R_2 = \ \, \frac{V_{ref}}{V_0} \ \, \left( R_1 + R_2 \right) \ \cong \ \, \frac{7.0 \ V}{V_0} \ \, \left( R_1 + R_2 \right) \label{eq:R2}$$

$$0 \leq C_{ref} \leq 0.1~\mu F$$

;  $R_3 \cong R_1 \parallel R_2$

Selection of Q1 based on considerations of Section 4.

Values shown are for a 15 V, 500 mA regulator using an unheatsinked MC1723CP and a 2N3055 on a 6°C/W heatsink for  $T_A$  up to + 70°C.

Figure 3-5A. MC1723C PNP Boost Configuration

$$\begin{split} R_{SC} &\cong \ \frac{0.66 \ V}{I_{SC}} \ ; \ 10 \ k\Omega < R_1 + R_2 < 100 \ k\Omega \ ; \ 0 \leq C_{ref} \leq 0.1 \ \mu F \\ R_2 &= \ \frac{V_{ref}}{V_0} \ (R_1 + R_2) \cong \ \frac{7.0 \ V}{V_0} \ (R_1 + R_2) \\ R_3 &= R_1 \ || \ R_2 \end{split}$$

$0 < R_4 \le V_{BE}$  on (Q1) / 5.0 mA

Selection of Q1 based on considerations of Section 4.

Values shown are for a 12 V, 750 mA regulator using an unheatsinked MC1723CP and a 2N3791 on a 4°C/W heatsink for  $T_A$  up to + 70°C.

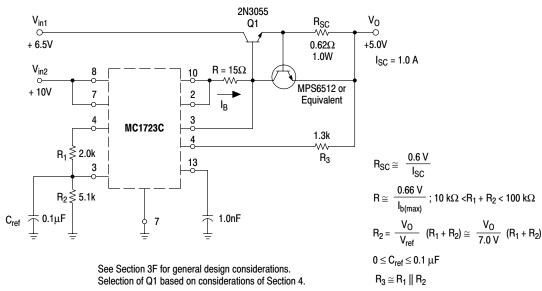

#### 3. High Efficiency Regulator Configurations

When large output currents at voltages under approximately 9.0 V are desired, the configuration of Figure 3–6A can be utilized to obtain increased operating efficiency. This is accomplished by providing a separate low voltage input supply for the pass element. This method, however, usually necessitates that separate short circuit protection be provided for the IC regulator and external pass element. Figure 3–6A shows a high efficiency regulator configuration for the MC1723C.

Figure 3-6A. MC1723C High Efficiency Regulator Configuration

Values shown for a 5.0 V, 1.0 A regulator using an unheatsinked MC1723CP and a 2N3055 on a 10°C/W heatsink for  $T_A$  up to + 70°C.

#### B. Negative, Adjustable Output IC Regulator Configurations

#### 1. Basic Regulator Configurations (MC1723C)

Although a positive regulator, the MC1723C can be used in a negative regulator circuit configuration. This is done by using an external pass element and a zener level shifter as shown in Figure 3–1B. It should be noted that for proper operation, the input supply must not vary over a wide range, since the correct value for  $V_Z$  depends directly on this voltage. In addition, it should be noted that this circuit will not operate with a shorted output.

Figure 3-1B. MC1723C Negative Regulator Configuration

$$|V_{\Omega}| \ge 10 \text{ V}$$

;  $10 \text{ k}\Omega \le R_1 + R_2 \le 100 \text{ k}\Omega$

$$R_2 = \frac{V_{ref}}{|V_0|} (R_1 + R_2) \cong \frac{7.0 \text{ V}}{|V_0|} (R_1 + R_2)$$

$$V_Z \leq |V_{in}| - V_{BE(Q1)} - 3.0 \ V; \ V_Z \geq \ |V_{in}| - \ |V_O| - V_{BE(Q1)} + 6.0 \ V$$

Selection of Q1 based on considerations of Section 4.

Values shown are for a -15 V, 750 mA regulator using the MC1723CP with Q1 mounted on a  $20^{\circ}$ C/W heatsink at  $T_A$  up to  $+70^{\circ}$ C. **Do not short circuit output.**

#### C. Positive, Fixed Output IC Regulator Configurations

#### 1. Basic Regulator Configuration

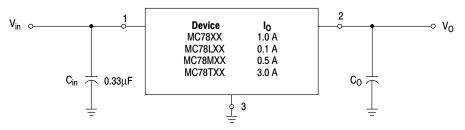

The basic current configuration for the positive three–terminal regulators is shown in Figure 3–1C. Depending on which regulator type is used, this configuration can provide output currents in excess of 3.0 A.

#### 2. Output Current Boosting

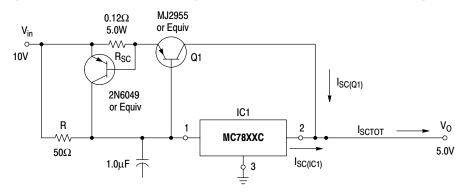

Figure 3–2C illustrates a method for obtaining greater output currents with the three–terminal positive regulators. Although any of these regulators may be used, usually it is most economical to use the 1.0 A MC7800C in this configuration.

Figure 3-1C. Basic Circuit Configuration for Positive, Fixed Output, Three-Terminal Regulators

$C_{in}$ : required if regulator is located more than a few (=2 to 4) inches away from input supply capacitor; for long input leads to regulator, up to 1.0  $\mu F$  may be needed for  $C_{in}$ . ( $C_{in}$  should be a high frequency type capacitor.)

C<sub>O</sub>: improves transient response.

XX: two digits of type number indicating nominal output voltage.

See Section 15 for heatsinking.

Figure 3-2C. Current Boost Configuration for Positive Three-Terminal Regulators

XX: two digits of type number indicating nominal output voltage.

R: used to divert IC regulator bias current and determines at what output current level Q1 begins conducting.

$$0 < R \le \frac{V_{BE \quad on(Q1)}}{I_{Bias \ (IC1)}} \; ; \; R_{SC} \approx \; \frac{0.6 \ V}{I_{SC(Q1)}} \; ; \; I_{SCTOT} = I_{SC(Q1)} + I_{SC(IC1)}$$

Selection of Q1 based on considerations of Section 4.

Values shown are for a 5.0 V, 5.0 A regulator using an MC7805CT on a 2.5°C/W heatsink and Q1 on a 1°C/W heatsink for  $T_A$  up to 70°C.

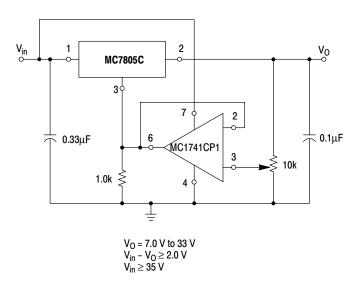

#### 3. Obtaining an Adjustable Output Voltage

With the addition of an op amp, an adjustable output voltage supply can be obtained with the MC7805C. Regulation characteristics of the three–terminal regulators are retained in this configuration, shown in Figure 3–3C. If lower output currents are required, then an MC78M05C (0.5 A) could be used in place of the MC7805C.

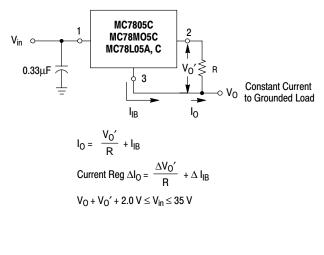

#### 4. Current Regulator

In addition to providing voltage regulation, the three–terminal positive regulators can also be used as current regulators to provide a constant current source. Figure 3–4C shows this configuration. The output current can be adjusted to any value from  $\approx$  8.0 mA ( $I_Q$ , the regulator bias current) up to the available output current of the regulator. Five–volt regulators should be used to obtain the greatest output voltage compliance range for a given input voltage.

Figure 3–3C. Adjustable Output Voltage Configuration Using a Three–Terminal Positive Regulator

Figure 3–4C. Current Regulator Configuration

#### 5. High Input Voltage

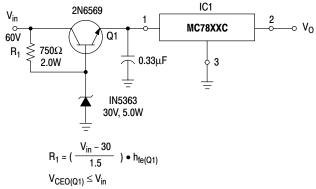

Occasionally, it may be necessary to power a three–terminal regulator from a supply voltage greater than  $V_{in(max)}$ , 35 V or 40 V. In these cases a preregulator circuit, as shown in Figure 3–5C, may be used.

Figure 3–5C. Preregulator for Input Voltages Above  $V_{\text{in}(\text{max})}$

$\ensuremath{\mathsf{XX}}\xspace$  two digits of type number indicating nominal output voltage.

Values shown for V<sub>in</sub> = 60 V

Q1 should be mounted on a 2°C/W heatsink for operation at  $T_A$  up to +70°C. IC1 should be appropriately heatsinked for the package type used.

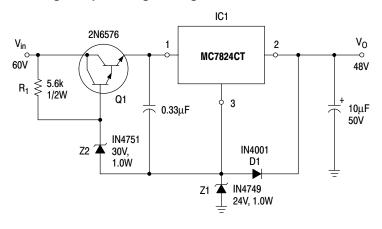

#### 6. High Output Voltage

If output voltages above 24 V are desired, the circuit configuration of Figure 3–6C may be used. Zener diode (Z1) sets the output voltage, while Q1, Z2, and D1 assure that the MC7824C does not have more than 30 V across it during short circuit conditions.

Figure 3-6C. High Output Voltage Configuration for Three-Terminal Positive Regulators

$$V_0 = V_{Z1} + 24$$

;  $R_1 = (\frac{V_{in} - (V_{Z1} + V_{Z2})}{1.5}) \bullet h_{fe(Q2)}$

Values shown are for a 48 V, 1.0 A regulator Q1 mounted on a 10°C/W heatsink and IC1 mounted on a 2°C/W heatsink for  $T_A$  up to +70°C.

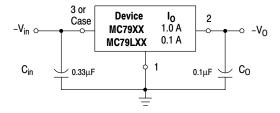

#### D. Negative, Fixed Output IC Regulator Configurations

#### 1. Basic Regulator Configurations

Figure 3-1D gives the basic circuit configuration for the MC79XX and MC79LXX three-terminal negative regulators.

Figure 3-1D. Basic Circuit Configuration for Negative Three-Terminal Regulators

$C_{in}$ : required if regulator is located more than a few ( $\approx$  2 to 4) inches away from input supply capacitor; for long input leads to regulator, up to 1.0 µF may be required. Cin should be a high frequency type

$\begin{array}{l} \text{$C_0$: improves stability and transient response.} \\ \text{$XX$: two digits of type number indicating nominal output voltage.} \end{array}$

See Section 15 for heatsinking.

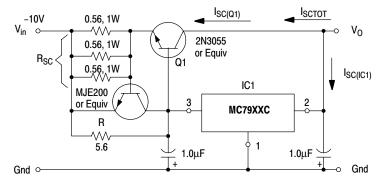

#### **Output Current Boosting**

In order to obtain increased output current capability from the negative three–terminal regulators, the current boost configuration of Figure 3–2D may be used. Currents which can be obtained with this configuration are limited only by the capabilities of the external pass transistor(s).

Figure 3–2D. Output Current Boost Configuration for Three–Terminal Negative Regulators

XX: two digits of type number indicating output voltage. See Section 2 for available voltages.

R: used to divert regulator bias current and determine at what output current level Q1 begins conducting.

$$\begin{split} 0 < R \leq & \frac{V_{BE - on(Q1)}}{I_{Bias(IC1)}} \\ I_{SCTOT} = & I_{SC(Q1)} + I_{SC(IC1)} \\ R_{SC} \approx & \frac{0.6 \text{ V}}{I_{SC}} \end{split}$$

Selection of Q1 based on considerations of Section 4.

Values shown are for a -5.0 V, +4.0 A regulator; using an MC7905CT on a  $1.5^{\circ}$ C/W heatsink with Q1 mounted on a  $1^{\circ}$ C/W heatsink for  $T_{\Delta}$  up to  $+70^{\circ}$ C.

#### 2. Current Regulator

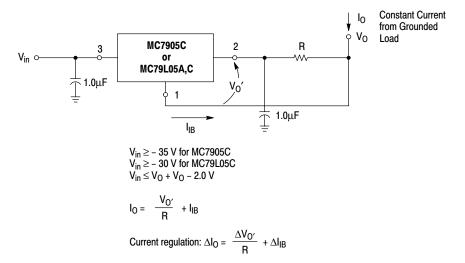

The three–terminal negative regulators may also be used to provide a constant current sink, as shown in Figure 3–3D. In order to obtain the greatest output voltage compliance range at a given input voltage, the MC7905C or MC79L05C should be used in this configuration.

Figure 3-3D. Current Regulator Configuration for the Three-Terminal Negative Regulators

#### F. General Design Considerations

In addition to the design equations given in the regulator circuit configuration panels of Sections 3A-E, there are a few general design considerations which apply to all regulator circuits. These considerations are given below.

#### 1. Regulator Voltages

For any circuit configuration, the worse-case voltages present on each pin of the IC regulator must be within the maximum and/or minimum limits specified on the device data sheets. These limits are instantaneous values, not averages.

They include: a. V<sub>in(min)</sub>

- b.  $V_{in(max)}$

- c.  $(V_{in} V_{out})_{min}$

- d. V<sub>out(min)</sub>

- e. V<sub>out(max)</sub>

For example, the voltage between Pins 12 and 7 (V<sub>in</sub>) of an MC1723CP must never fall below 9.5 V, even instantaneously, or the regulator will not function properly, (see Figure 3–1B).

#### 2. Regulator Power Dissipation, Junction Temperature and Safe Operating Area

The junction temperature, power dissipation output current or safe operating area limits of the IC regulator *must never be exceeded*.

#### 3. Operation with a Load Common to a Voltage of Opposite Polarity

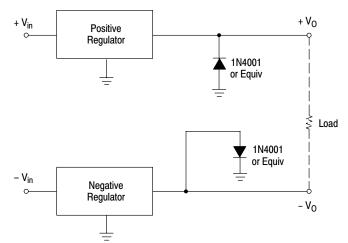

In many cases, a regulator powers a load which is not connected to ground but instead is connected to a voltage source of opposite polarity (e.g. op amps, level shifting circuits, etc.). In these cases, a clamp diode should be connected to the regulator output as shown in Figure 3–1F. This protects the regulator, during startup and short circuit operation, from output polarity reversals.

Figure 3-1F. Output Polarity Reversal Protection

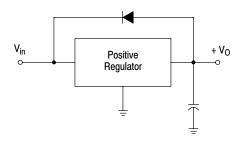

#### 4. Reverse Bias Protection

Occasionally, there exists the possibility that the input voltage to the regulator can collapse faster than the output voltage. This could occur, for example, if the input supply is "crowbarred" during an output overvoltage condition. If the output voltage is greater  $\approx 7.0$  V, the emitter–base junction of the series pass element (internal or external) could break down and be damaged. To prevent this, a diode shunt can be employed, as shown in Figure 3–2F.

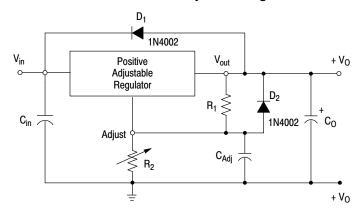

Figure 3–3F shows a three–terminal positive–adjustable regulator with the recommended protection diodes for output voltages in excess of 25 V, or high output capacitance values ( $C_O > 25 \,\mu\text{F}$ ,  $C_{Adj} > 10 \,\mu\text{F}$ ). Diode D1 prevents  $C_O$  from discharging through the regulator during an input short circuit. Diode D2 protects against capacitor  $C_{Adj}$  from discharging through the regulator during an output short circuit. The combination of diodes D1 and D2 prevents  $C_{Adj}$  from discharging through the regulator during an input short circuit.

Figure 3-2F. Reverse Bias Protection

Figure 3–3F. Reverse Bias Protection for Three–Terminal Adjustable Regulators

#### **SECTION 4**

## SERIES PASS ELEMENT CONSIDERATIONS FOR LINEAR REGULATORS

Presently, most monolithic IC voltage regulators that are available have output current capabilities from 100 mA to 3.0 A. If greater current capability is required, or if the IC regulator does not possess sufficient safe—operating—area (SOA), the addition of an external series pass element is necessary.

In this section, configurations, specifications and current limit techniques for external series pass elements will be considered. For illustrative purposes, pass elements for only positive regulator types will be discussed. However, the same considerations apply for pass elements used with negative regulators.

#### A. Series Pass Element Configurations

#### **Using an NPN Type Transistor**

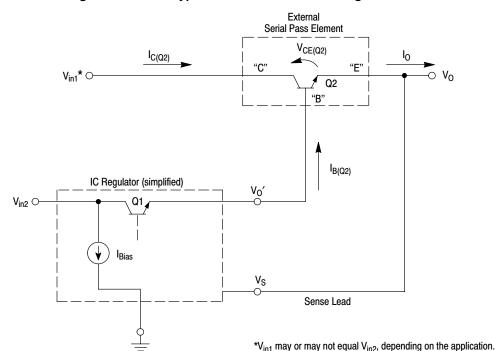

If the IC regulator has an external sense lead, an NPN type series pass element may be used, as shown in Figure 4–1 A. This pass element could be a single transistor or multiple transistors arranged in Darlington and/or paralleled configurations.

In this configuration, the IC regulator supplies the base current ( $I_B$ ) to the pass element (Q2) which acts as a current amplifier and provides the increased output current ( $I_D$ ) capability.

Figure 4-1A. NPN Type Series Pass Element Configuration

#### **Using a PNP Type Transistor**

If the IC regulator does not have an external sense lead, as in the case of the three–terminal fixed output regulators, the configuration of Figure 4–1B can be used. (Regulators which possess an external sense lead may also be used with this configuration.) As before, the PNP type pass element can be a single transistor or multiple transistors.

External

Series Pass Element

V<sub>CE(Q2)</sub>

"E"

"B"

IC Regulator (simplified)

V<sub>In1</sub>

V<sub>In2</sub>

Figure 4–1B. PNP Type Series Pass Element Configuration

This configuration functions in a similar manner to that of Figure 4–1A, in that the regulator supplies base current to pass element. The resistor (R) serves to route the IC regulator bias current ( $I_{Bias}$ ) away from the base of Q2. If not included, regulation would be lost at low output currents. The value of R is low enough to prevent Q2 from turning on when  $I_{Bias}$  flows through this resistor, and is given by:

$$0 < R \le \frac{V_{BEon}(Q2)}{I_{Bias}}$$

(4.0)

#### **B. Series Pass Element Specifications**

Independent of which configuration is utilized, the transistor or transistors that compose the pass element must have adequate ratings for  $I_{C(max)}$ ,  $V_{CEO}$ ,  $h_{fe}$ , power dissipation, and safe operating area.

1.  $I_{C(max)}$  for the pass element of Figure 4–1A,  $I_{C(max)}$  is given by:

$$I_{C(max)(Q2)} \ge I_{O(max)} - I_{B(max)(Q2)} = I_{O(max)} - \frac{I_{C(max)(Q2)}}{h_{fe(Q2)}}$$

(4.1)

$$\geq I_{O(max)}$$

(4.2)

For the configuration of Figure 4–1B:

$$I_{C(max)(Q2)} \ge I_{O(max)} + I_{B(max)(Q2)}$$

(4.3)

$$\geq I_{O(max)}$$

(4.4)

**2.**  $V_{CEO}$  — since  $V_{CE(Q2)}$  is equal to  $V_{in1(max)}$  when the output is shorted or during start up:

$$V_{CEO(Q2)} \le V_{in1(max)} \tag{4.5}$$

3. h<sub>fe</sub> — the minimum DC current gain for Q2 in Figures 4–1A and 4–1B is given by:

$$h_{fe(min)(Q2)} \ge \frac{I_{C(max)(Q2)}}{I_{B(max)(Q2)}} @ V_{CE} = (V_{in1(min)} - V_O)$$

(4.6)

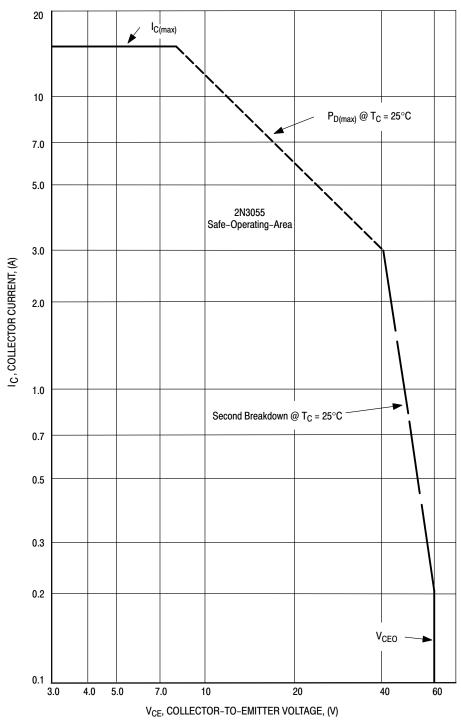

#### 4. Maximum Power Dissipation P<sub>D(max)</sub>, and Safe Operating Area (SOA)

For any transistor there are certain combinations of  $I_C$  and  $V_{CE}$  at which it may safely be operated. When plotted on a graph, whose axes are  $V_{CE}$  and  $I_C$ , a safe–operating region is formed.

As an example, the safe–operating–area (SOA) curve for the well known 2N3055 NPN silicon power transistor is shown in Figure 4–2. The boundaries of the SOA curve are formed by  $I_{C(max)}$ , power dissipation, second breakdown and  $V_{CEO}$  ratings of the transistor. Notice that the power dissipation and second breakdown ratings are given for a case temperature of +25°C and must be derated at higher case temperatures. (Derating factors may be found in the transistors' data sheets.) These boundaries must never be exceeded during operation, or destruction of the transistor(s) which constitute the pass element may result. (In addition, the maximum operating junction temperature *must not be exceeded*, see Section 15.)

#### C. Current Limiting Techniques

In order to select a transistor or transistors with adequate SOA, the locus of pass element  $I_C$  and  $V_{CE}$  operating points must be known. This locus of points is determined by the input voltage ( $V_{in1}$ , output voltage ( $V_O$ ), output current ( $I_O$ ) and the type of output current limiting technique employed.

In most cases, V<sub>in1</sub>, V<sub>O</sub>, and the required output current are already known. All that is left to determine is how the chosen current limit scheme affects required pass element SOA.

Note, since the external pass element is merely an extension of the IC regulator, the following discussions apply equally well to IC regulators not using an external pass element.

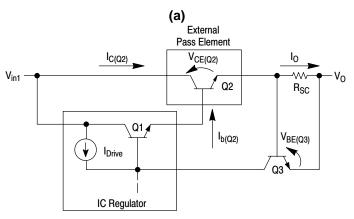

#### 1. Constant Current Limiting

This method is the simplest to implement and is extensively used, especially at the lower output current levels. The basic circuit configuration is shown in Figure 4–3A, and operates in the following manner.

As the output current increases, the voltage drop across  $R_{SC}$  increases, proportionately. When the output current has increased to the point that the voltage drop across  $R_{SC}$  is equal to the base–emitter ON voltage of Q3 ( $V_{BEon}(Q3)$ ), Q3 conducts. This diverts base current ( $I_{Drive}$ ) away from Q1, the IC regulator's internal series pass element. Base drive ( $I_{B(Q2)}$ ) of Q2 is therefore reduced and its collector–emitter voltage increases, thereby reducing the output voltage below its regulated value,  $V_{out}$ . The resulting output voltage–current characteristic is shown in Figure 4–3B.

The value of I<sub>SC</sub> is given by:

$$I_{SC} = \frac{V_{BEon(Q3)}}{R_{SC}}$$

(4.7)

Figure 4–2. 2N3055 Safe Operating Area (SOA)

Figure 4-3. Constant Current Limiting

By using the base of Q1 in the IC regulator as a control point, this configuration has the added benefit of limiting the IC regulator output current ( $I_{B(Q2)}$ ) to  $I_{SC}/h_{fe(Q2)}$ , as well as limiting the collector current of Q2 to  $I_{SC}$ . Of course, access to this point is necessary. Fortunately, it is usually available in the form of a separate pin or as the regulator's compensation terminal.<sup>(1)</sup>

The required safe-operating-area for Q2 can be obtained by plotting the V<sub>CE</sub> and I<sub>C</sub> of Q2 given by:

$$V_{CE(Q2)} = V_{in1} - V_O - I_O R_{SC} \simeq V_{in1} - V_O$$

(4.8)

$$I_{C(Q2)} \simeq I_{O} \tag{4.9}$$

where,

$$V_O = V_{out}$$

for  $0 \le I_O \le I_{SC}$  (4.10)

and,

$$I_O = I_{SC}$$

for  $0 \le V_O \le V_{out}$  (4.11)

The resulting plot is shown in Figure 4–4. The transistor chosen for Q2 must have an SOA which encloses this plot, see Figure 4–4. Note that the greatest demand on the transistor's SOA capability occurs when the output of the regulator is short circuited and the pass element must support the full input voltage and short circuit current simultaneously.

Figure 4–4. Constant Current Limit SOA Requirements

(1) The three—terminal regulators have internal current limiting and therefore do not provide access to this point. If an external pass element is used with these regulators, constant current limiting can still be accomplished by diverting pass element drive.

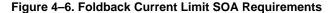

#### 2. Foldback Current Limiting

A disadvantage of the constant current limit technique is that in order to obtain sufficient SOA the pass element must have a much greater collector current capability than is actually needed. If the short circuit current could be reduced, while still allowing full output current to be obtained during normal regulator operation, more efficient utilization of the pass elements SOA capability would result. This can be done by using a "foldback" current limiting technique instead of constant current limiting.

The basic circuit configuration for this method is shown in Figure 4–5(A). The circuit operates in a manner similar to that of the constant current limiting circuit, in that output current control is obtained by diverting base drive away from Q1 with Q3.

At low output currents,  $V_A$  approximately equals  $V_O$  and  $V_{R2}$  is less than than  $V_O$ . Q3 is therefore non–conducting and the output voltage remains constant. As the output current increases, the voltage drop across  $R_{SC}$  increases until  $V_A$  and  $V_{R2}$  are great enough to bias Q3 on. The output current at which this occurs is  $I_K$ , the "knee" current.

(b) (a) External Pass Element  $I_{C(Q2)}$ V<sub>CE(Q2)</sub>  $V_{out}$ V<sub>O</sub>, OUTPUT VOLTAGE  $V_{in1}$  $\mathsf{R}_{\mathsf{SC}}$ Isc ≶R₁ Q1. I<sub>Drive</sub> IO, OUTPUT CURRENT IC Regulator  $V_{BE(Q3)}$

Figure 4-5. Foldback Current Limiting

The output voltage will now decrease. Less output current is now required to keep  $V_A$  and  $V_{R2}$  at a level sufficient to bias Q3 on since the voltage at its emitter has the tendency to decrease faster than that at its base. The output current will continue to "foldback" as the output voltage decreases, until an output short circuit current level ( $I_{SC}$ ) is reached when the output voltage is zero. The resulting output current–voltage characteristic is shown in Figure 4–5B. The values for  $R_1$ ,  $R_2$ , and  $R_{SC}$  (neglecting base current of Q3) are given by:

$$R_{SC} = \frac{V_{out}/I_{SC}}{\left(1 + \frac{V_{out}}{V_{BEon(Q3)}}\right) - \frac{I_{K}}{I_{SC}}}$$

(4.12)

$$\frac{R_2}{R_1 + R_2} = \frac{V_{BEon(Q3)}}{I_{SC} R_{SC}}$$

(4.13)

and,

$$R_1 + R_2 \le I_{\text{Drive}}^{\text{Vout}}$$

(4.14)

where: V<sub>out</sub> = normal regulator output voltage

$I_K$  = knee current

I<sub>SC</sub> = short circuit current

I<sub>Drive</sub> = base drive to regulator's internal pass element(s)

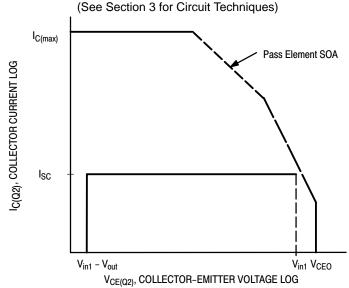

A plot of Q2 operating points, which result when using this technique, is shown in Figure 4–6. Note that the pass element is required to operate with a collector current of only  $I_{SC}$  during short circuit conditions, not the full output current,  $I_K$ . This results in a more efficient utilization of the SOA of Q2 allowing the use of a smaller transistor than if constant current limiting were used. Although foldback current limiting allows use of smaller pass element transistors for a given regulator output current than does constant current limiting, it does have a few disadvantages.

Referring to Equation (4.12), as the foldback ratio ( $I_K/I_{SC}$ ) is increased, the required value of  $R_{SC}$  increases. This results in a greater input voltage at higher foldback ratios. In addition, it can be seen for Equation (4.12) that there exists an absolute limit to the foldback ratio equal to:

$$\left(\frac{I_K}{I_{SC(max)}}\right) = 1 + \frac{V_{out}}{V_{BEon(Q3)}} \text{ for } R_{SC} = \infty$$

(4.15)

For these reasons, foldback ratios greater than 2:1 or 3:1 are not usually practical for the lower output voltage regulators.

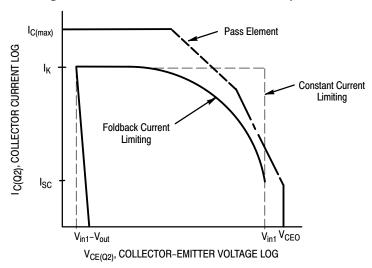

#### D. Paralleling Pass Element Transistors

Occasionally, it will not be possible to obtain a transistor with sufficient safe—operating—area. In these cases it is necessary to parallel two or more transistors. Even if a single transistor with sufficient capability is available, it is possible that paralleling two smaller transistors is more economical.

In order to insure that the collector currents of the paralleled transistors are approximately equal, the configuration of Figure 4–7 can be used. Emitter–ballasting resistors are used to force collector–current sharing between Q1 and Q2. The collector–current mismatch can be determined by considering the following, from Figure 4–7,

$$V_{BE1} + V_1 = V_{BE2} + V_2$$

(4.16)

and,

$$\Delta V_{BE} = \Delta V$$

(4.17)

where:  $V_{BE} = V_{BE1} - V_{BE2}$  and,  $\Delta V = V_2 - V_1$

Assuming  $I_{E1} \simeq I_{C1}$  and  $I_{E2} \simeq O_{C2}$ , the collector-current mismatch is given by,

$$\frac{I_{C2} - I_{C1}}{I_{C2}} = \frac{\left(\frac{V_2}{R_E}\right) - \left(\frac{V_1}{R_E}\right)}{\left(\frac{V_2}{R_E}\right)} = \frac{V_2 - V_1}{V_2} = \frac{\Delta V}{V_2} = \frac{\Delta V_{BE}}{V_2}$$

(4.18)

(4.19)

and, percent collector–current mismatch =

$$\frac{\Delta V_{BE}}{V_2} \times 100\%$$

(4.20)

From Equation (4.20), the collector–current mismatch is dependent on  $\Delta$  V<sub>BE</sub> and V<sub>2</sub>. Since  $\Delta$ V<sub>BE</sub> is usually acceptable, V<sub>2</sub> should be 1.0 V to 0.5 V, respectively. R<sub>E</sub> is therefore given by:

$$R_{E} = \frac{0.5 \text{ V to } 1.0 \text{ V}}{I_{C1}} = \frac{0.5 \text{ V to } 1.0 \text{ V}}{I_{C2}} = \frac{0.5 \text{ V to } 1.0 \text{ V}}{I_{C}/2}$$

(4.21)

Figure 4.7 Barallaling Base Flamout Transistors

# SECTION 5 LINEAR REGULATOR CONSTRUCTION AND LAYOUT

An important, and often neglected, aspect of the total regulator circuit design is the actual layout and component placement of the circuit. In order to obtain excellent transient response performance, high frequency transistors are used in modern integrated circuit voltage regulators. Proper attention to circuit layout is therefore necessary to prevent regulator instability or oscillations, or degraded performance.

In this section, guidelines will be given on proper regulator layout and placement of circuit components. In addition, topics such as remote voltage sensing, semiconductor mounting techniques, and thermal system evaluations will also be discussed.

#### 1. General Layout and Component Placement Considerations

As mentioned previously, modern integrated circuit regulators are necessarily high bandwidth devices in order to obtain good transient response characteristics. To insure stable closed–loop operation, all these devices are frequency compensated, either internally or externally. This compensation can easily be upset by unwanted stray circuit capacitances and lead inductances, resulting in spurious oscillations. Therefore, it is important that the circuit lead lengths be short and the layout as tight as possible. Particular attention should be paid to locating the compensation and bypass capacitors as close to the IC as possible. Lead lengths associated with the external pass element(s), if used, should also be minimized.

Often overlooked is the stray inductance associated with the input leads to the regulator circuit. If the lead length from the input supply filter capacitor to the regulator input is more than a couple of inches, a 0.01  $\mu$ F to 1.0  $\mu$ F high frequency type capacitor (tantalum, ceramic, etc.) should be used to bypass the supply leads close to the regulator input pins.

#### 2. Ground Loops and Remote Voltage Sensing

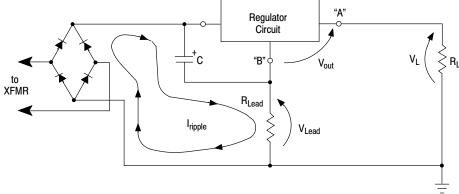

**Ground Loops** — Regulator performance can also suffer if ground loops in the circuit wiring are not avoided. The most common ground loop problem occurs when the return lead of the input supply filter capacitor is improperly located, as shown in Figure 5–1. If this return lead is physically connected between the load return and the regulator circuit ground point ("B"), a ripple voltage component (60 Hz or 120 Hz) can be induced on the load voltage (V<sub>L</sub>). This is due to the high peaks of the filter capacitor ripple current (I<sub>ripple</sub>) flowing through the lead resistance between the load and regulator. These peaks can be 5 to 15 times the value of load current. Since the regulator will only keep constant the voltage between its sense lead and ground point, points "A" and "B" in Figure 5–1, this additional ripple voltage (V<sub>lead</sub>), will appear at the load.

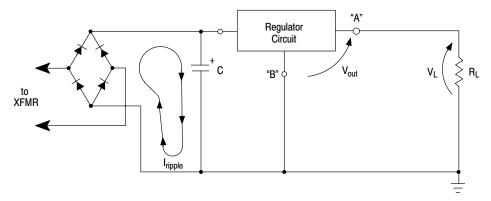

This problem can be avoided by proper placement and connection of the filter capacitor return load as shown in Figure 5–2.

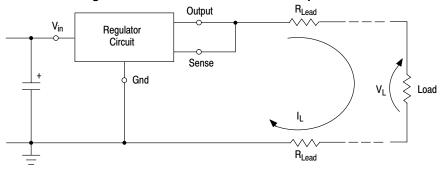

Remote Voltage Sensing — Closely related to the above ground loop problem is resistance in the current carrying leads to the load. This can cause poorer than expected load regulation in cases where the load currents are large or where the load is located some distance from the regulator. This is illustrated in Figure 5–3. As stated previously, the regulator circuit will keep the voltage present between its sense and ground pins constant. From Figure 5–3 we can see that any lead resistance between these points and the load will cause the load voltage (V<sub>L</sub>) to vary with varying load current, I<sub>L</sub>. This effectively lowers the load regulation of the circuit.

Figure 5–1. Filter Capacitor Ground Loop — WRONG!

Figure 5–2. Filter Capacitor Ground Loop — RIGHT!

This problem can be avoided by the use of remote Sense leads, as shown in Figure 5–4. The voltage drops in the high current carrying leads now have no effect on the load voltage (V<sub>L</sub>). However, since the Sense and Ground leads are usually rather long, care must be exercised that their associated lead inductance is minimized, or loop instability may result. The Ground and Sense leads should be formed into a twisted pair lead to minimize their lead inductance and noise pickup.

Figure 5-3. Effects of Resistance In Output Leads

Figure 5-4. Remote Voltage Sensing

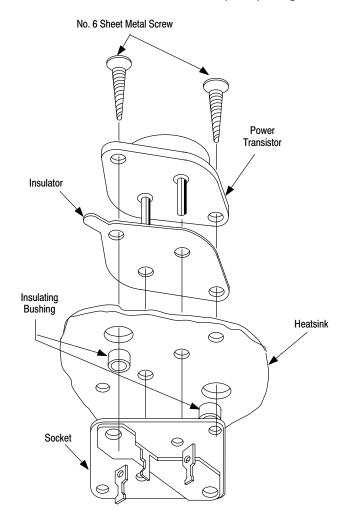

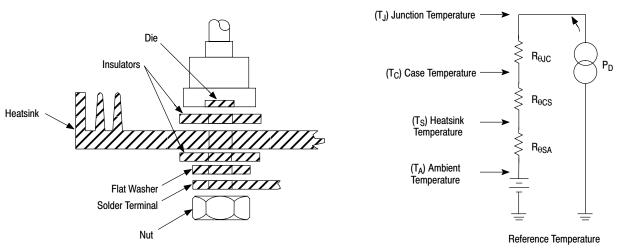

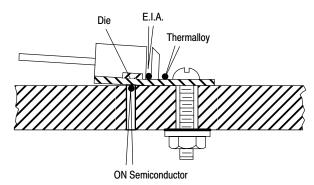

#### 3. Mounting Considerations for Power Semiconductors

Current and power ratings of semiconductors are inseparably linked to their thermal environment. Except for lead–mounted parts used at low currents, a heat exchanger is required to prevent the junction temperature from exceeding its rated limit, thereby running the risk of a high failure rate. Furthermore, the semiconductor industry's field history indicated that the failure rate of most silicon semiconductors decreases approximately by one–half for a decrease in junction temperature from 160° to 135°C.<sup>(1)</sup> Guidelines for designers of military power supplies impose a 110°C limit upon junction temperature.<sup>(2)</sup> Proper mounting minimizes the temperature gradient between the semiconductor case and the heat exchanger.

Most early life field failures of power semiconductors can be traced to faulty mounting procedures. With metal packaged devices, faulty mounting generally causes unnecessarily high junction temperature, resulting in reduced component lifetime, although mechanical damage has occurred on occasion from improperly mounting to a warped surface. With the widespread use of various plastic packaged semiconductors, the prospect of mechanical damage is very significant. Mechanical damage can impair the case moisture resistance or crack the semiconductor die.

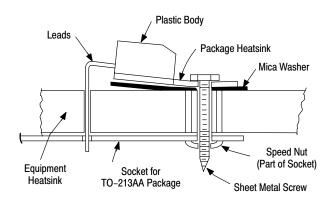

Figure 5–5 shows an example of doing nearly everything wrong. A tab mount TO–220 package is shown being used as a replacement for a TO–213AA (TO–66) part which was socket mounted. To use the socket, the leads are bent — an operation which, if not properly done, can crack the package, break the internal bonding wires, or crack the die. The package is fastened with a sheet metal screw through a 1/4" hole containing a fiber–insulating sleeve. The force used to tighten the screw tends to pull the package into the hole, possibly causing enough distortion to crack the die. In addition the contact area is small because of the area consumed by the large hole and the bowing of the package, the result is a much higher junction temperature than expected. If a rough heatsink surface and/or burrs around the hole were displayed in the illustration, most but not all poor mounting practices would be covered.

Figure 5–5. Extreme Case of Improperly Mounting a Semiconductor (Distortion Exaggerated)

5801 Tabor Ave., Philadelphia, PA 19120.

Cho-Therm is a registered trademark of Chromerics, Inc. Grafoil is a registered trademark of Union Carbide

Kapton is a registered trademark of E.I. Dupont Rubber–Duc is a trademark of AAVID Engineering

Sil Pad is a trademark of Berquist

Sync-Nut is a trademark of ITW Shakeproof

Thermasil is a registered trademark and Thermafilm is a trademark of Thermalloy, Inc.

ICePAK, Full Pak, POWERTAP and Thermopad are trademarks of ON Semiconductor, Inc.

<sup>(1)</sup> MIL-HANDBOOK — 2178, SECTION 2.2.

<sup>(2)</sup> Navy Power Supply Reliability — Design and Manufacturing Guidelines NAVMAT P4855–1, Dec. 1982 NAVPUBFORCEN,

In many situations the case of the semiconductor must be electrically isolated from its mounting surface. The isolation material is, to some extent, a thermal isolator as well, which raises junction operating temperatures. In addition, the possibility of arc—over problems is introduced if high voltages are present. Various regulating agencies also impose creepage distance specifications which further complicates design. Electrical isolation thus places additional demands upon the mounting procedure.

Proper mounting procedures usually necessitate orderly attention to the following:

- 1. Preparing the mounting surface

- 2. Applying a thermal grease (if required)

- 3. Installing the insulator (if electrical isolation is desired)

- 4. Fastening the assembly

- 5. Connecting the terminals to the circuit

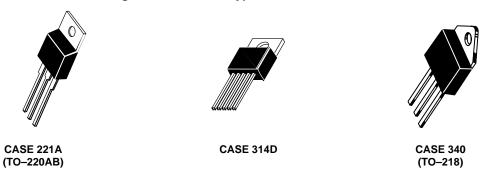

In this note, mounting procedures are discussed in general terms for several generic classes of packages. As newer packages are developed, it is probable that they will fit into the generic classes discussed in this note. Unique requirements are given on data sheets pertaining to the particular package. The following classes are defined:

Flange Mount Tab Mount

Plastic Body Mount Surface Mount

Appendix A contains a brief review of thermal resistance concepts.

Appendix B discusses measurement difficulties with interface thermal resistance tests.

#### **Mounting Surface Preparation**

In general, the heatsink mounting surface should have a flatness and finish comparable to that of the semiconductor package. In lower power applications, the heatsink surface is satisfactory if it appears flat against a straight edge and is free from deep scratches. In high power applications, a more detailed examination of the surface is required. Mounting holes and surface treatment must also be considered.

#### **Surface Flatness**

Surface flatness is determined by comparing the variance in height ( $\Delta h$ ) of the test specimen to that of a reference standard as indicated in Figure 5–6. Flatness is normally specified as a fraction of the Total Indicator Reading (TIR). The mounting surface flatness (i.e,  $\Delta h$ /TIR) if less than 4 mils per inch, normal for extruded aluminum, is satisfactory in most cases.

TIR = Total Indicator Reading

Sample

Piece

TIR

Ah

Reference

Piece

Device Mounting Area

Figure 5-6. Surface Flatness Measurement

#### **Surface Finish**

Surface finish is the average of the deviations both above and below the mean value of surface height. For minimum interface resistance, a finish in the range of 50  $\mu$ in. to 60  $\mu$ in. is satisfactory. A finer finish is costly to achieve and does not significantly lower contact resistance. Tests conducted by Thermalloy using a copper TO–204 (TO–3) package with a typical 32  $\mu$ in. finish, showed that heatsink finishes between 16  $\mu$ in. and 64  $\mu$ in. caused less than  $\pm 2.5\%$  difference in interface thermal resistance when the voids and scratches were filled with a thermal joint compound. (3) Most commercially available cast or extruded heatsinks will require spotfacing when used in high power applications. In general, milled or machined surfaces are satisfactory if prepared with tools in good working condition.

#### **Mounting Holes**

Mounting holes generally should only be large enough to allow clearance of the fastener. The larger thick flange type packages having mounting holes removed from the semiconductor die location, such as the TO–204AA, may successfully be used with larger holes to accommodate an insulating bushing, but many plastic encapsulated packages are intolerant of this condition. For these packages, a smaller screw size must be used such that the hole for the bushing does not exceed the hole in the package.

Punched mounting holes have been a source of trouble because if not properly done, the area around a punched hole is depressed in the process. This "crater" in the heatsink around the mounting hole can cause two problems. The device can be damaged by distortion of the package as the mounting pressure attempts to conform it to the shape of the heatsink indentation, or the device may only bridge the crater and leave a significant percentage of its heat–dissipating surface out of contact with the heatsink. The first effect may often be detected immediately by visual cracks in the package (if plastic), but usually an unnatural stress is imposed, which results in an early–life failure. The second effect results in hotter operation and is not manifested until much later.

Although punched holes are seldom acceptable in the relatively thick material used for extruded aluminum heatsinks, several manufacturers are capable of properly utilizing the capabilities inherent in both fine—edge blanking or sheared—through holes when applied to sheet metal as commonly used for stamped heatsinks. The holes are pierced using Class A progressive dies mounted on four—post die sets equipped with proper pressure pads and holding fixtures.

When mounting holes are drilled, a general practice with extruded aluminum, surface cleanup is important. Chamfers must be avoided because they reduce heat transfer surface and increase mounting stress. However, the edges must be broken to remove burrs which cause poor contact between device and heatsink and may puncture isolation material.

#### **Surface Treatment**

Many aluminum heatsinks are black—anodized to improve radiation ability and prevent corrosion. Anodizing results in significant electrical but negligible thermal insulation. It need only be removed from the mounting area when electrical contact is required. Heatsinks are also available which have a nickel plated copper insert under the semiconductor mounting area. No treatment of this surface is necessary.

Another treated aluminum finish is iridite, or chromate—acid dip, which offers low resistance because of its thin surface, yet has good electrical properties because it resists oxidation. It need only be cleaned of the oils and films that collect in the manufacture and storage of the sinks, a practice which should be applied to all heatsinks.

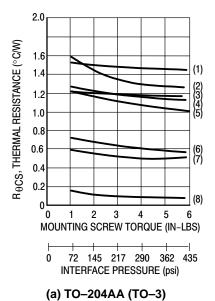

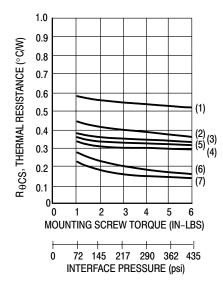

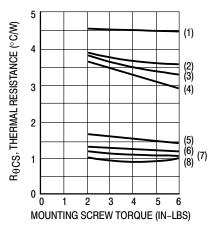

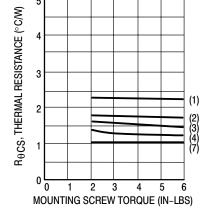

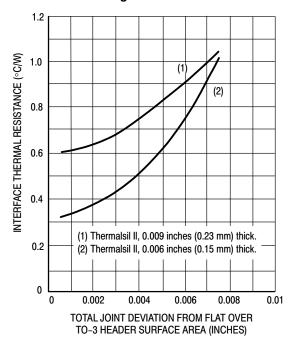

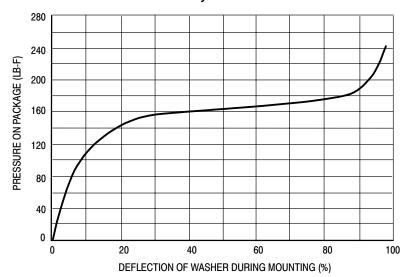

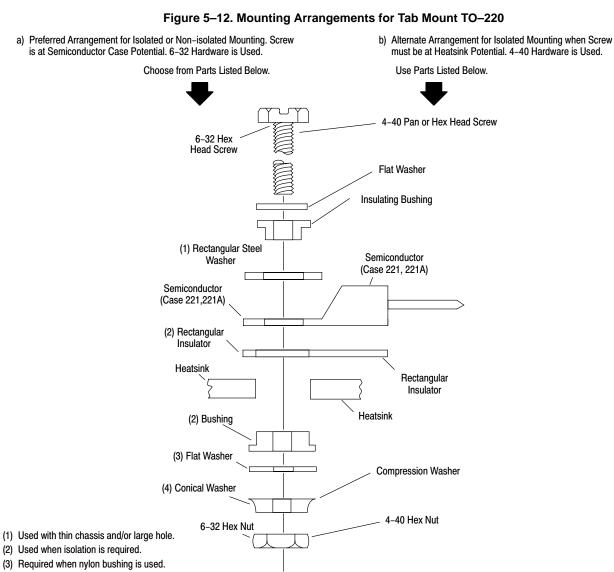

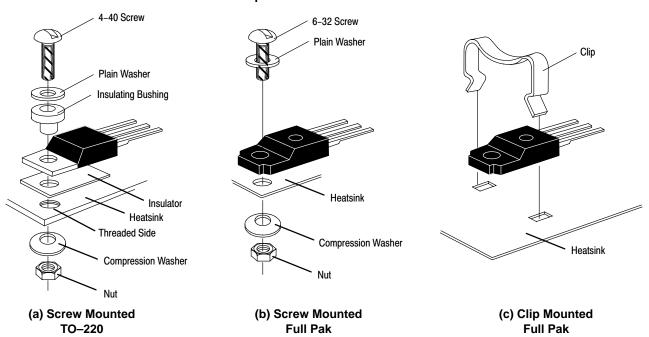

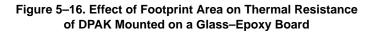

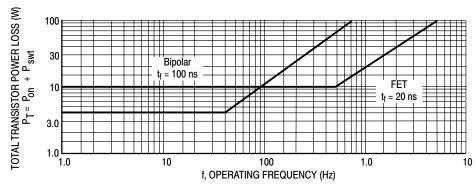

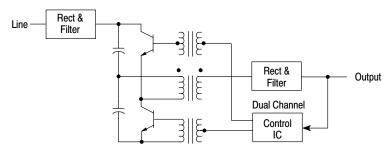

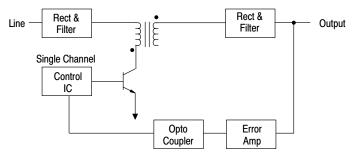

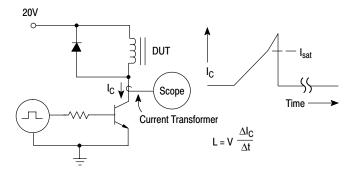

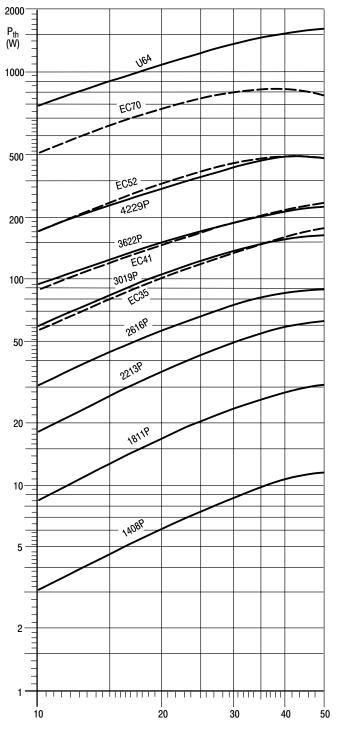

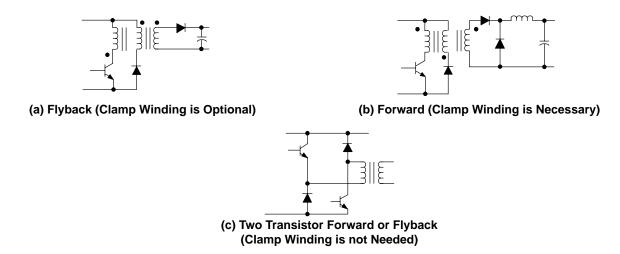

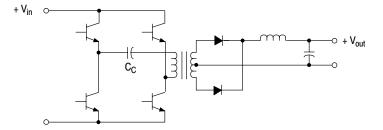

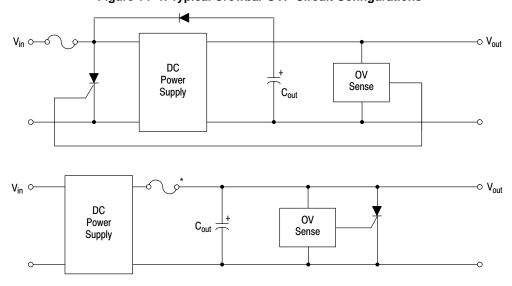

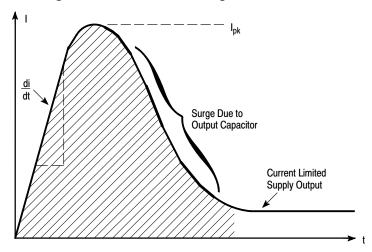

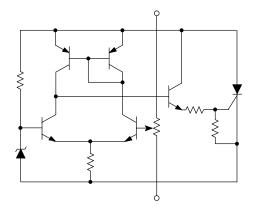

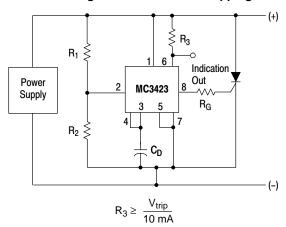

For economy, paint is sometimes used for sinks; removal of the paint where the semiconductor is attached is usually required because of the paint's high thermal resistance. However, when it is necessary to insulate the semiconductor package from the heatsink, hard anodized or painted surfaces allow an easy installation for low voltage applications. Some manufacturers will provide anodized or painted surfaces meeting specific insulation voltage requirements, usually up to 400 V.