## INSTITUTO POLITÉCNICO DE TOMAR

Engenharia Electrotécnica

## Exame de Recurso de Sistemas Digitais

## 11 de Setembro de 2003

## **PARTE PRÁTICA**

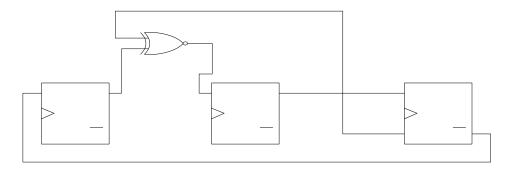

- 1. Projecte um contador binário de 3 bits, que realize a sequência dos números pares, no sentido ascendente (0-2-4-6-0). O salto de um estado para o outro é controlado pelo valor de uma entrada Enable que quando está a zero permite o salto para o valor seguinte e quando está a 1 volta para o estado 0. **Nota: Deve garantir que o circuito é auto-corrector.**

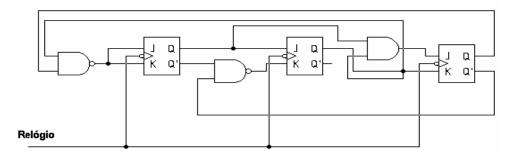

- 2. Analise o seguinte circuito, determinando o seu diagrama de estados. Considere o bit A (flip-flop mais à direita) como o menos significativo.

3. Represente o diagrama temporal das saídas dos três flip-flops (Q<sub>0</sub>, Q<sub>1</sub>, Q<sub>2</sub>,), durante seis transições de relógio. O estado inicial das saídas é "0". (Apresente os cálculos que efectuar, caso contrário a resposta não será validada). Considere o bit 2 (flip-flop mais à direita) como o menos significativo.